ADIUVO ENGINEERING & TRAINING LTD. - FPGA systems

https://www.adiuvoengineering.com/ https://www.fpgahorizons.com/

Adiuvo designs FPGA systems for the some of the biggest names in the aerospace sector, as well as delivering consultancy, training and marketing services to leading chip manufacturers and other clients.

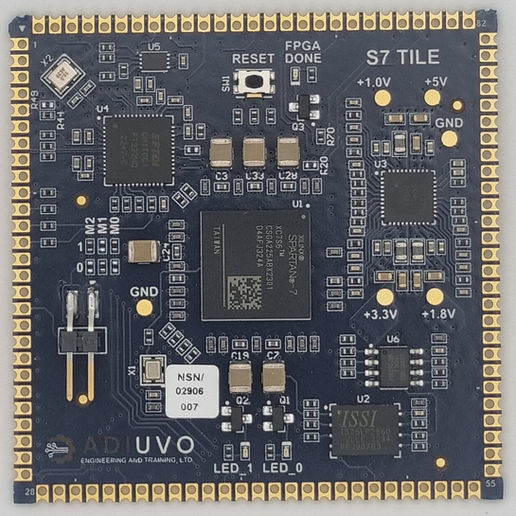

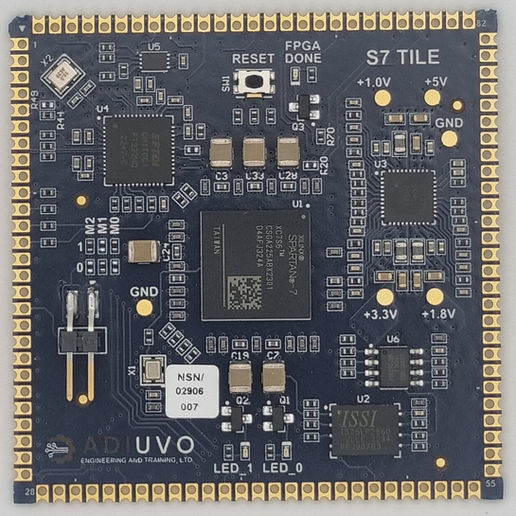

Astria Embedded System Tile.

The Astria Embedded System Tile provides developer with a risk free way of integrating a Spartan 7 in their design without the worry of designing a chip down solution.

The tile measures 59mm x 59 mm and provides the following

Supply voltage 4.5 to 18V

Spartan 7 XC7S25 with 23,360 Logic Cells, 80 DSP, 45 BRAM

Configuration Memory 256Mbit QSPI

Done LED

Two user LED

USB JTAG - Connector needed on carrier board

100 MHz Oscillator

Reset Button

Boot selection header (JTAG/QSPI)

PSRAM – 32Mbit – Seral RAM connected to the FPGA

82 IO including – Power and Ground, JTAG, 32 IO at 3v3, 41 IO configurable voltage (3v3-1.2V and LVDS)

To help get started using the Astria Embedded System Tile the following is provided

User guide

Schematic

Vivado Board definition

Reference Designs - Including IP to enable processor to access FPGA internals using processor UART / SPI

Tile footprint in Altium to help accelerate your design.

This information is presented on our public repository and Adiuvo can be contracted to develop your application or assist with it.

TYPICAL APPLICATIONS WHICH WOULD BENEFIT FROM THE TILE

System Controller – Power supply sequencing, power monitoring, configuration management, board management and supervision / communication interface.

Protocol conversion – Convert to and from bespoke / legacy protocol.

Sensor Aggregation – Aggregate several different sensor types for easy access by processor

IO expansion – Provide additional interfaces e.g. QSPI, SPI, I2C etc.

Processing offloading – e.g. Control algorithm e.g. PID, Filtering, co processing , encryption / decryption of data streams entering and leaving system

Health and Usage Monitoring systems – Integrate with sensors e.g. accelerometer, pressure, humidity etc to monitor the environmental operating conditions.

Rapid Prototyping – quickly demonstrate the concept required in a FPGA. Reduces risk of FPGA integration / Removes obsolescence management issues